架構(gòu) 文章 最新資訊

架構(gòu)介紹

架構(gòu)

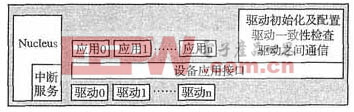

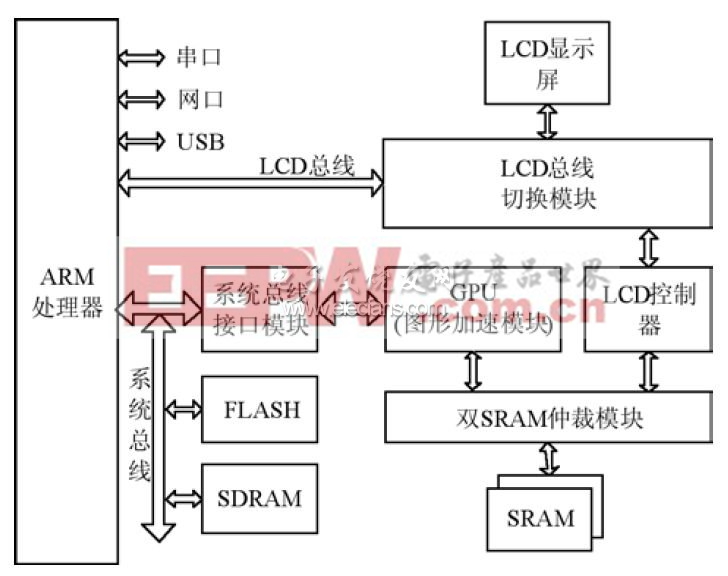

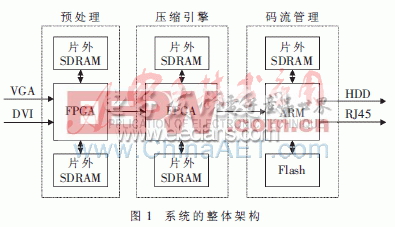

架構(gòu),又名軟件架構(gòu),是有關(guān)軟件整體結(jié)構(gòu)與組件的抽象描述,用于指導(dǎo)大型軟件系統(tǒng)各個(gè)方面的設(shè)計(jì)。架構(gòu)描述語言(ADL)用于描述軟件的體系架構(gòu)?,F(xiàn)在已有多種架構(gòu)描述語言,如Wright(由卡內(nèi)基梅隆大學(xué)開發(fā)),Acme(由卡內(nèi)基梅隆大學(xué)開發(fā)),C2(由UCI開發(fā)),Darwin(由倫敦帝國學(xué)院開發(fā))。ADL的基本構(gòu)成包括組件、連接器和配置。

中文名架構(gòu)

外文名Software [ 查看詳細(xì) ]

相關(guān)主題

熱門主題

關(guān)于我們 -

廣告服務(wù) -

企業(yè)會(huì)員服務(wù) -

網(wǎng)站地圖 -

聯(lián)系我們 -

征稿 -

友情鏈接 -

手機(jī)EEPW

Copyright ?2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《電子產(chǎn)品世界》雜志社 版權(quán)所有 北京東曉國際技術(shù)信息咨詢有限公司

京ICP備12027778號(hào)-2 北京市公安局備案:1101082052 京公網(wǎng)安備11010802012473

京ICP備12027778號(hào)-2 北京市公安局備案:1101082052 京公網(wǎng)安備11010802012473

Copyright ?2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《電子產(chǎn)品世界》雜志社 版權(quán)所有 北京東曉國際技術(shù)信息咨詢有限公司